6541 ROM manufactured by MOS Technology

- IC number

- 6541

- IC function

- 16 kbit (2k×8) ROM with two chip selects

- Related components

- 16 kbit (2k×8) ROM with five chip selects

| IC number | Manufacturer | Documentation |

|---|---|---|

| 6541 | MOS Technology | Preliminary Datasheet July 1977 |

| IC number | Package | Access time |

|---|---|---|

| 6541 | 24-pin DIP | 300 ns |

Details

The 6541 16K Read Only Memory is a monolithic N-channel metal-gate array manufactured with a low-threshold process and utilizing both enhancement and depletion mode MOS transistors.Three-state outputs provide bus-compatibility with microprocessor-based memory systems. The ROM's are organized as 2048 words of 8 bits each.

Features

Maximum ratings

| Rating | Symbol | Voltage | Unit |

|---|---|---|---|

| Supply Voltage | VCC | -0.3 to +7.0 | V |

| Input/Output Voltage | VIN | -0.3 to +7.0 | V |

| Operating Temperature | TOP | 0 to 70 | °C |

| Storage Temperature | TSTG | -55 to +150 | °C |

Electrical Characteristics

| Characteristic | Symbol | Min. | Typ. | Max. | Unit |

|---|---|---|---|---|---|

| Input High Voltage | VIH | VSS+2.0 | - | VCC | V |

| Input Low Voltage | VIH | VSS-.3 | - | VSS+.8 | V |

| Input Leakage Current (A0-A10, CS1, CS2, Ø2) | IIN | 1.0 | 2.5 | µA | |

| Input Current for High Impedance (Three State) Outputs: VIN = 0.4V to 2.4V | ITSI | 1.0 | 10 | µA | |

| Output High Voltage: VCC = Min ILOAD <= -100µA | VOH | VSS+2.4 | V | ||

| Output Low Voltage: VCC = Min ILOAD <= 1.6mA | VOL | VSS+.4 | V | ||

| Output Low Current (sinking) VOL <= .4V | IOL | 1.6 | mA | ||

| Supply Current | ICC | 110 | 150 | mA |

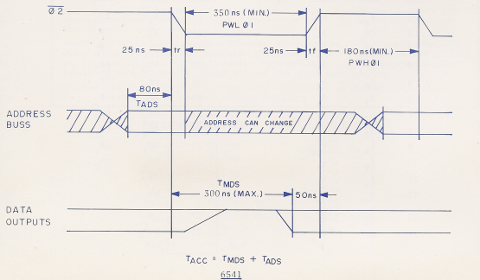

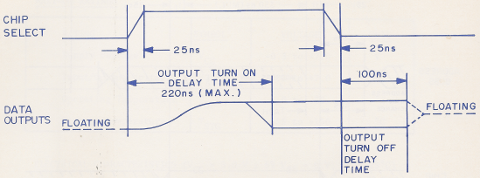

Timing

Copyright © 2005-2010 Ronald van Dijk - All rights reserved

Sources:

MOS Technology 6540/6541 Preliminary Datasheet July 1977

Last update: 13 May 2010